# Lateral versus Interdigitated Diode Design for 10 Gb/s Low-Voltage Low-Loss Silicon Ring Modulators

M. Pantouvaki, H. Yu<sup>1</sup>, P. Verheyen, G. Lepage, W. Bogaerts<sup>1</sup>, M. Moelants, J. Wouters, D. Radisic, A. Vandervorst, P. Absil and J. Van Campenhout

imec, Kapeldreef 75, 3001, Leuven, Belgium

Photonics Research Group, Dept. of Information Technology, Ghent University – imec, Center of Nano- and Biophotonics (NB Photonics),St.

Pietersnieuwstraat 41, 9000 Ghent, Belgium

Author e-mail address:pantouvm@imec.be

**Abstract:** Silicon ring modulators with interdigitated diodes demonstrate 7.5 dB extinction ratios at 3 dB insertion loss for 1 V<sub>pp</sub>, a 4.5 dB improvement over the lateral diode design, and can operate up to 10 Gb/s.

Silicon ring optical modulators are attracting increasing interest for low energy, small footprint optical interconnects co-integrated with CMOS electronics. Key requirements for such devices are high extinction ratio, low insertion loss, high modulation efficiency, multi-Gb/s speed and low energy per bit. Recently, 10 Gb/s and 25 Gb/s optical modulation has been reported in carrier-depletion ring modulators using a 1 V peak-to-peak driving voltage  $(V_{pp})$  [1, 2]. However, the obtained extinction ratios were limited to 5dB for insertion losses lower than 3dB. Such modulators are typically designed with the depletion area parallel to the waveguide (lateral diode design). Modulators with junctions perpendicular to the waveguide (interdigitated diode design) have been proposed to increase the modulation efficiency and extinction ratio, however so far they required high voltage swings  $V_{pp}$ , incompatible with CMOS [3, 4]. In this work we compare the performance of two identical ring modulators, differing only in the diode design. We find that the interdigitated design results in higher modulation efficiency, achieving a 7.5 dB extinction ratio for 3 dB insertion loss using 1  $V_{pp}$ , as opposed to only 3 dB extinction ratio with the lateral diode design. Open eye diagrams were obtained at 10 Gb/s for both modulator types.

The silicon ring modulators were fabricated on 200 mm Silicon-On-Insulator (SOI) wafers with 220 nm thick crystalline silicon on 2  $\mu$ m thick buried oxide. Rings of 40  $\mu$ m radius were defined by 193 nm lithography and dry etching of 70 nm Si. 248 nm lithography was subsequently used to define the p- and n-doping patterns as shown in Figure 1(a). Conventional back-end-of line W contacts and Cu metal interconnects were used for wiring.

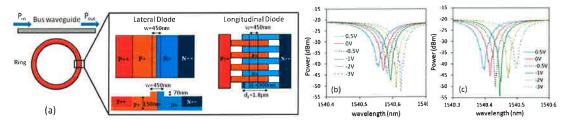

Figure 1: a) Lateral versus interdigitated diode design. b) Transmitted power versus wavelength of silicon ring modulators with lateral and c) interdigitated diode design, for different applied bias.

Figure 1(a) shows the two diode designs that were investigated on ring modulators with identical dimensions of 450 nm waveguide width, 570 nm gap between the ring and the bus waveguide, and nominal doping densities of 0.8e18cm<sup>-3</sup> for both p and n dopants. The first was the typical lateral diode design, where the p- and n-doped areas are parallel to the ring waveguide, and the second was the interdigitated pattern, where the p- and n-doped areas are periodically interleaved perpendicularly to the ring. The width of the fingers in this case was 300 nm for both p- and n-doping, while the interaction length was d<sub>1</sub> = 1.8 µm for each finger. This resulted in a low-frequency capacitance of ~380 fF at 0 V for rings with the longitudinal design as opposed to 97 fF for the lateral design, and a series resistance of ~20 Ohm for both. Transmission spectra for different bias conditions of the lateral and interdigitated designs are shown in Figures 1(b) and 1(c). The experimental quality factors Q were 15400 and 18700 for the lateral and interdigitated designs respectively. Consequently, the calculated 3 dB cut-off frequency for these devices was 12.5 GHz for the lateral design, limited by the cavity photon lifetime, and 6 GHz for the longitudinal design limited by the RC time constant when driven from a 50 Ohm transmission line.

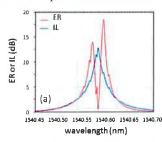

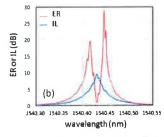

Figure 2 shows the static extinction ratio at  $V_{pp}$  and the corresponding insertion loss versus wavelength for lateral and interdigitated modulator design. While both modulators are capable of high extinction ratios at resonance,

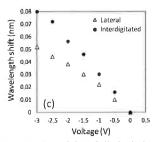

the interdigitated diode design results in smaller losses for higher extinction ratios. In particular, maximum extinction ratios of 18.5 dB and 29 dB were measured for lateral and interdigitated modulators, corresponding to insertion losses of 7.9 dB and 4.8 dB respectively. More specifically, for an insertion loss of 3 dB, the extinction ratios for the lateral and interdigitated patterns were 3 dB and 7.5 dB respectively. Figure 2(c) shows the resonance wavelength shift of the two designs with applied bias. While the modulation efficiency was 22 pm/V for the lateral design, this was increased to 30 pm/V for the interdigitated design.

Eye diagrams from both devices generated at 10 Gb/s using 1.2  $V_{pp}$  at -1 V DC bias and a pseudo-random bit sequence (PRBS) of  $2^{15}$ -1 are shown in Figure 3. Considering the capacitance of each device, this corresponds to an energy consumption of about 31 fJ/bit and 117 fJ/bit for the lateral and interdigitated devices respectively. Both eyes are open with dynamic extinction ratios in excess of 10 dB. However, the horizontal eye opening of the interdigitated modulator is suffering from the RC frequency limitation of this device. This speed limitation can be improved by reducing the interaction length of the diode fingers ( $d_1$ ). If the interaction length is limited to the waveguide area, a reduction in capacitance and power consumption by a factor of up to 3 is expected, without a substantial penalty on the extinction ratio and insertion loss. In addition, shrinking the ring radius will help to lower the power consumption in future devices.

Figure 2: Extinction ratio and insertion loss versus wavelength at 1  $V_{pp}$  for a) lateral and b) interdigitated diode design. The extinction ratios corresponding to 3 dB insertion loss are indicated by the shadowed areas in each plot. c) Comparison of resonance wavelength shift with applied voltage for lateral and interdigitated diode design.

Figure 3: 10 Gb/s optical eye diagrams at 1.2  $V_{pp}$  of ring modulators with (a) lateral and (b) interdigitated diode design.

In conclusion, a comparison of silicon ring modulators differing only in the diode design was made. Extinction ratios of 3 dB and 7.5 dB for an insertion loss of 3 dB and driving voltage 1  $V_{pp}$  were obtained with the lateral and the interdigitated diode design respectively. Both devices generated open-eye diagrams at 10 Gb/s, although this modulation speed is close to the RC limit for the current interdigitated-diode design.

The authors acknowledge the efforts of imec's 200-mm pline for their contributions to the device fabrication. This work was supported by imec's Core Partner Program.

#### References

[1] G. Li, X. Zheng, J. Yao, H. Thacker, I. Shubin, Y. Luo, K. Raj, J. E. Cunningham, and A. V. Krishnamoorthy, "25Gb/s 1V-driving CMOS ring modulator with integrated thermal tuning," Optics Express 19(21), 20435-443 (2011).

[2] P. Dong, Sh. Liao, H. Liang, W. Qian, X. Wang, R. Shafiiha, D. Feng, G. Li, X. Zheng, A. V. Krishnamoorthy, and M. Asghari, "High-speed and compact silicon modulator based on a racetrack resonator with a 1V drive voltage," Optics Letters 35(19), 3246-3248, (2010).

[3] M. Ziebell, D. Marris-Morini, Gilles Rasigade, P. Crozat, J.-M. Fedeli, P. Grosse, E. Cassan, and L Vivien, "Ten Gbit/s ring resonator silicon modulator based on interdigitated PN junctions," Optics Express 19, 14690-695 (2011).

[4] H. Yu, W. Bogaerts, K. Komorowska, R. Baets, D. Korn, L. Alloatti, D. Hillerkuss, C. Koos, W. Freude, J. Leuthold, J. Van Campenhout, P. Verheyen and P. Absil, "Comparison between carrier-depletion-based silicon modulators with different doping patterns," Optical Fiber Communication Conference 2012.

IEEE.org | IEEE Xplore Digital Library | IEEE Standards | IEEE Spectrum | More Sites

Access provided by: University of Gent Sign Out

Browse Conference Publications > Optical Interconnects Conferen ...

## **Optical Interconnects Conference, 2012 IEEE**

Date: 20-23 May 2012

You searched for: Pantouvaki

1 Results returned

Lateral versus interdigitated diode design for 10 Gb/s low-voltage low-loss silicon ring modulators

Pantouvakl, M.; Yu, H.; Verheyen, P.; Lepage, G.; Bogaerts, W.; Moelants, M.; Wouters, J.; Radisic, D.; Vandervorst, A.; Absil, P.; Van Campenhout, J.

Optical Interconnects Conference, 2012 IEEE

Digital Object Identifier: 10.1109/OIC.2012.6224455

Publication Year: 2012 . Page(s): 44 - 45

Publication Year: 2012, Page(s): 44 - 45

IEEE CONFERENCE PUBLICATIONS

Sign In | Create Account

**IEEE Account**

Purchase Details

**Profile Information**

Need Help?

Change Username/Password

**Payment Options**

**Communications Preferences**

US & Canada: +1 800 678 4333

Update Address

Order History

**Profession and Education**

Worldwide: +1 732 981 0060

**Access Purchased Documents**

**Technical Interests**

Contact & Support

About IEEE Xplore | Contact | Help | Terms of Use | Nondiscrimination Policy | Site Map | Privacy & Opting Out of Cookies

A non-profit organization, IEEE is the world's largest professional association for the advancement of technology.

© Copyright 2012 IEEE - All rights reserved. Use of this web site signifies your agreement to the terms and conditions.

IEEE.org | IEEE Xplore Digital Library | IEEE Standards | IEEE Spectrum | More Sites

Cart (0) | Create Accour

Sh

The world's largest professional association for the advancement of technology

Follow:

## 2012 IEEE Optical Interconnects Conference (OI)

#### Sponsored by Photonics Society - PHO

Interconnections within digital computing and switching systems today are often a critical performance bottleneck. The purpose of this Workshop is to determine the interconnection requirements of emerging and future computer and communications systems and to discuss state-of-the-art solutions in wired and wireless, optical and electrical interconnection technologies. Interconnection technologies are considered at the component, packaging, and systems level.

### **Conference Details**

Dates

20 May - 23 May 2012

Location

Eldorado Hotel & Spa

Santa Fe, NM, USA

Web site Contact

www.oi-ieee.org/

Megan Figueroa

IEEE/Photonics Society

445 Hoes Lane

USA Piscataway NJ 08854

+1 732 562 3895 +1 732 562 8434

m.figueroa@ieee.org

Conference # Attendance

120 **Publications** Download conference papers from

19002

**IEEEXplore**

Please see the conference Web site for full details.

Call for Papers for Conference Authors

Find details for paper and abstract submission. Search for call for papers on conference site

Conference Focus

Science

Back to search results